Projects

Explore my work in hardware systems, RTL development, embedded systems, and more.

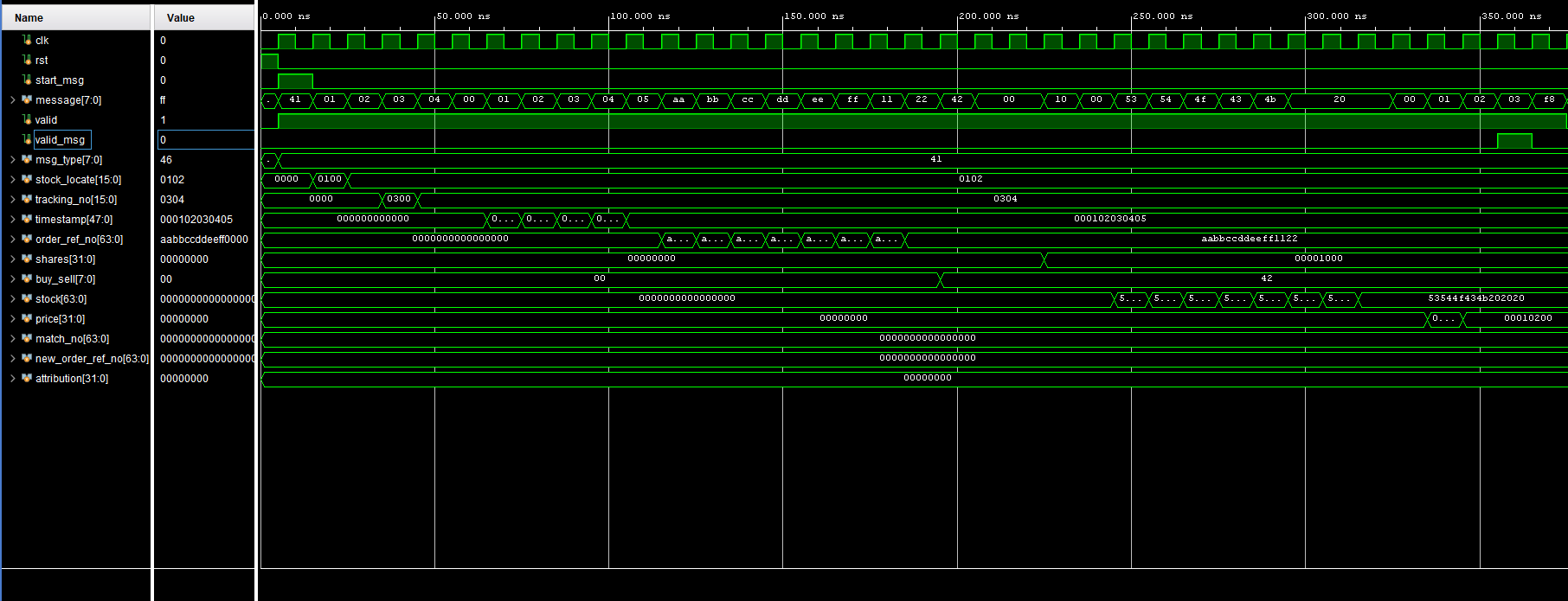

NASDAQ ITCH RTL Parser

We designed and verified an RTL parser for NASDAQ ITCH market data streams, supporting six of twenty-two message types. We implemented cycle-accurate logic to extract over ten fields, including multi-byte fields that span word boundaries. We built self-checking SystemVerilog testbenches with more than 150 directed and randomized test cases to validate field decoding, error handling, and message alignment.

More Info

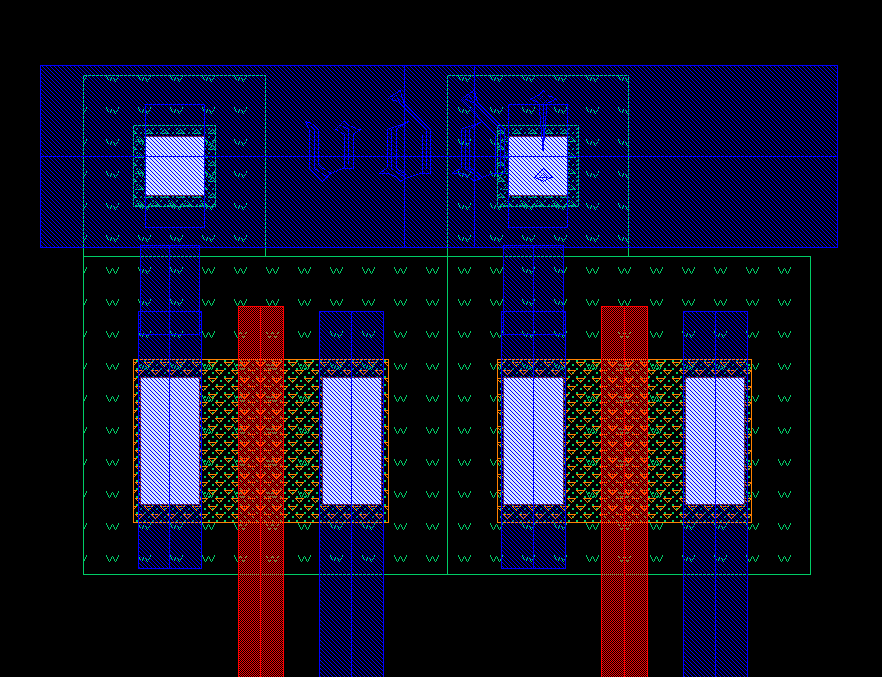

CMOS Inverter & Buffer Physical Design

I designed and built a CMOS inverter and buffer from the ground up, taking the project from schematic to physical layout. I simulated and verified the circuits, then optimized the layout to minimize area by 41% while ensuring all design rules and layout vs schematic checks passed.

More Info

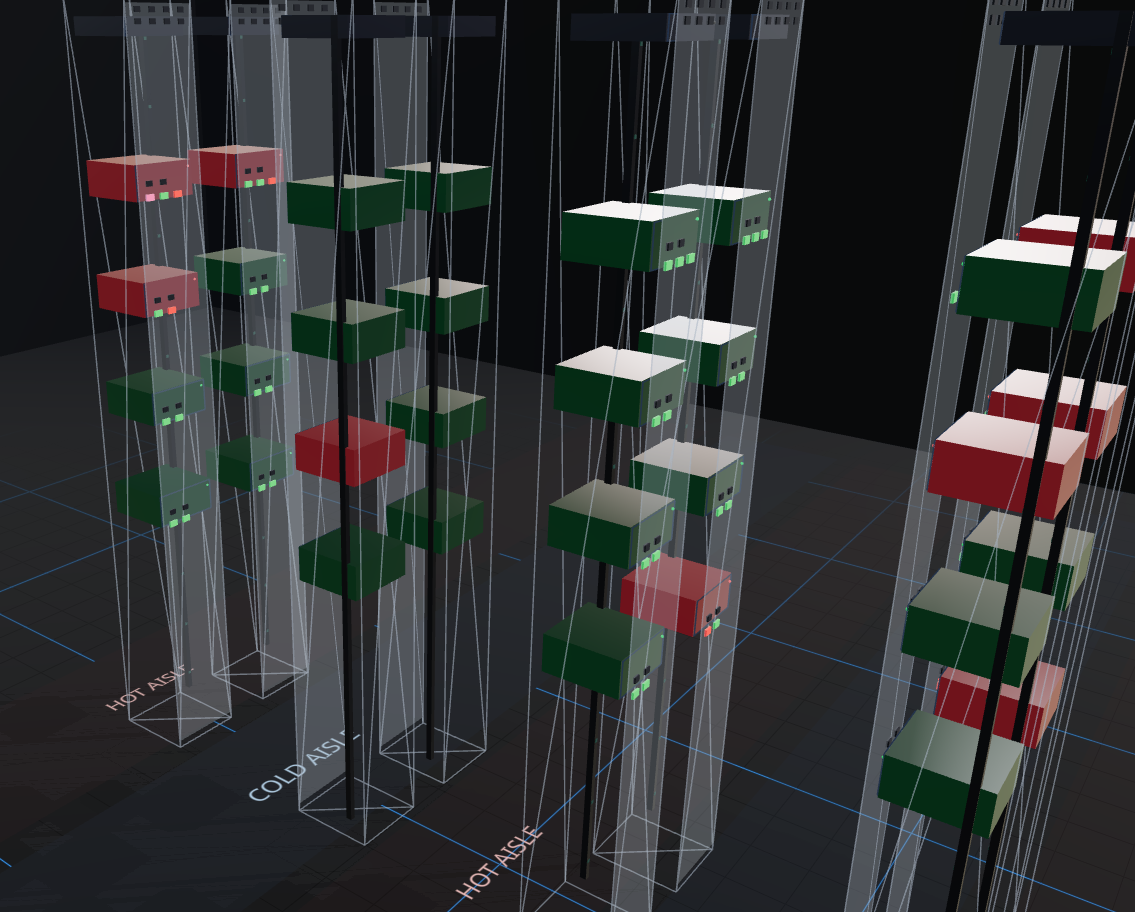

3D Datacenter Telemetry & Monitoring System

We built a 3D datacenter telemetry and monitoring system, simulating an 8-rack topology and capturing power, thermal, network, airflow, and storage data at 1 Hz. We implemented health-severity logic across five domains to track and visualize incidents in real time, and integrated Prometheus metrics with three Grafana dashboards, ensuring accurate and consistent data representation across the stack.

More Info

Urbana FPGA Rhythm Game Engine

We developed an FPGA-based rhythm game with 640×480 VGA at 60 Hz, PS/2 keyboard input, and 44.1 kHz audio playback. We designed the core RTL modules including the VGA controller, audio pipeline, and keyboard interface, integrated SD-card song loading for up to 10 tracks, and explored a MicroBlaze soft CPU for audio scheduling.

More Info

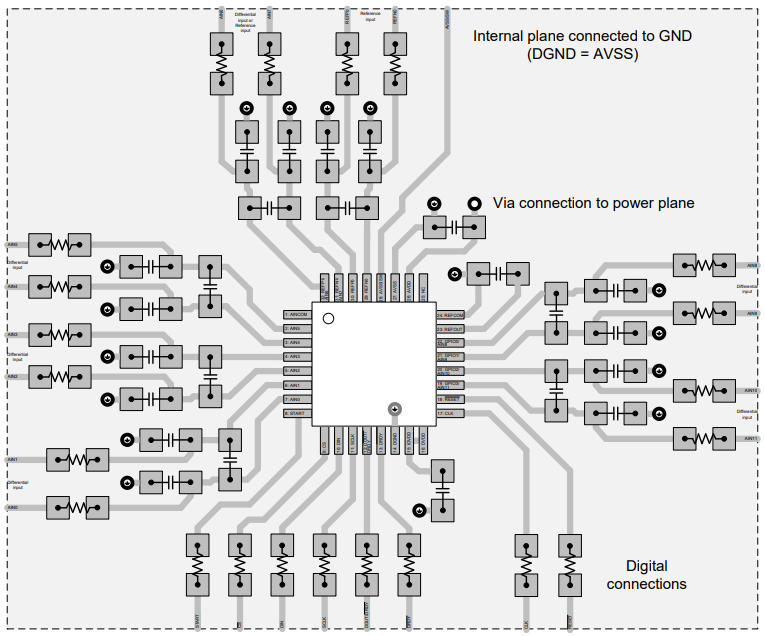

Custom ADC Board [FIS Electronic Team]

We designed a compact 8-channel, 24-bit ADC daughterboard sampling at 1 kHz and converting analog signals with high precision. We implemented SPI and I2C interfaces, applied RC input filtering for unipolar single-ended measurements, and carefully routed the PCB. The final 3.3 V modular board uses 0603 passives and castellated edges, reducing the footprint while enabling easy integration.

More Info